# Bee Style: Nov 2009:Bee Technologies

新製品情報

セミナー情報

デバイスモデル [トランジスタ] [CCFL]

回路解析シミュレーション [PSpice] PFC回路方式

道具箱 オシロスコープ・キット

外部セミナー情報

## 新製品情報

[デザインキット]

マイクロコントローラ(uPC494) による降圧回路

ステッピングモータドライブ回路

今回はデザインキットの新製品、2回路方式 のご紹介です。

(1)マイクロコントローラ(uPC494)による降圧 回路

uPC494はパルス幅制御方式スイッチング・レギュレータ用コントロール回路です。誤差増幅器の同相入力電圧範囲が広く、電圧帰還、過電流保護回路が容易に構成出来ます。このICのデバイスモデリングを行い、アプリケーション回路に組み込みました。この回路シミュレーションのテンプレートで色々なケースをシミュレーションできます。価格は105,000円(消費税込み)です。回路解析シミュレータは、PSpiceとなります。

### (2) ステッピングモータドライブ回路

TB62206FGはPWMチョッパ、2相バイポーラ駆動方式のステッピングモータドライブICです。BiCDプロセスを使用しています。このICのデバイスモデリングを行い、ステッピングモータは、周波数特性(インピーダンス特性)を等価回路モデルにて、アプリケーション回路に組み込みました。この回路シミュレーションのテンプレートで色々なケースをシミュレーションできます。また、ICの出力パワートランジスタをモデリングする事で、ノイズ解析も可能にしました。価格は210,000円(消費税込み)です。回路解析シミュレータは、PSpiceとなります。最新情報はWEBサイトをご参照下さい。

### セミナー情報

受動部品のスパイスモデルと シミュレーション

「受動部品のスパイスモデルとシミュレーション」のセミナーを開催致します。回路解析シミュレーションを行う場合、解析精度を向上させる為、受動部品を等価回路で考えることが重要になります。

例えばコンデンサは回路図上では、Cですが、実際にはESR(抵抗成分),ESL(インダクタンス成分)があります。これらを考慮する事で、確度の高い解析が出来ます。シミュレーションの解析精度は、実際の構成素子情報を反映させる事で、格段と向上します。ご好評の解説+体験学習のセミナー方式です。半導体部品のデバイスモデリングが正確なのに、シミュレーション結果と実機の波形及びノイズの波形が異なる方、受動部品のスパイスモデルの理解を深めたい方、回路解析シミュレーションにて、受動部品の影響を理解したい方に有効です。

#### プログラム:

1.受動部品のスパイスモデル 1.1コンデンサモデルについて 1.2インダクタンスモデルについて 1.3コンデンサのシミュレーションを体験する 1.4インダクタンスのシミュレーションを体験 する

2.回路方式における受動部品の影響2.1ケース・スタディで体験する

次ページに続きます。

マイクロコントローラ(uPC494)による降圧回路の詳細情報は、http://beetech.web.infoseek.co.jp/products/design/design\_07.htmlをご参照下さい。また、ステッピングモータドライブ回路の詳細情報は、http://beetech.web.infoseek.co.jp/products/design/design\_08.htmlをご参照下さい。サイトにデザインキットの解説書等をPDF形式で公開しています。

開催日:2009年11月27日(金曜日)

14:00-16:00 場所:JAJJ会議室

住所:〒105-0012 東京都港区芝大門二丁目

2番7号 7セントラルビル4階

電話:03-5401-3851

定員:4名

持参:ノートPCにOrCAD Capture,PSpiceの評

価版をセットアップしてきて下さい。

受講料:5,250円

お申し込み先(メールアドレス):

info@bee-tech.com

## デバイスモデル [トランジスタ]

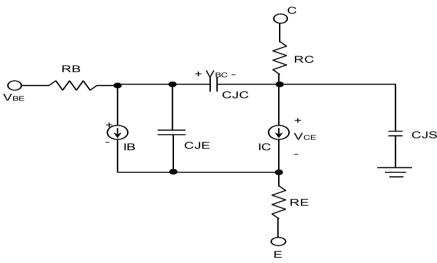

Fig.1 Gummel-Poonモデル

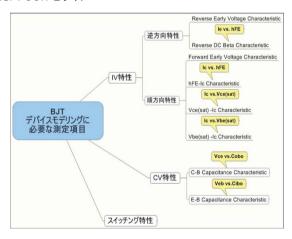

ビー・テクノロジーが提供するトランジスタのモデルはGummel-Poonモデル(Fig.1)です。Ebers-Mollモデルもありますが、殆ど流通していません。現在のEbers-Mollモデルの用途は、フォトカプラの等価回路モデルのトランジスタ出力側として採用される事があります。しかし、最近は、フォトカプラの出力側も解析精度を向上させたいユーザーは多く、Gummel-Poonモデルを採用するケースも増えてきました。流通している Gummel-Poonモデルは、順方向特性のみのモデルが多く、ビー・テクノロジーでは、順方向特性及び逆方向特性に再現性があるデバイスモデリングを実施し、提供しています。再現性のある項目について、Fig.2にマインドマップとしてまとめました。

Fig.2 再現性のある項目

Gummel-Poonモデル(電荷蓄積効果制御モデル)の基本的な考え方です。Gummel-Poonモデルのモデリングは、電気的特性図からモデルパラメータを抽出していきます。各電気的特性図とパラメータの関係は下記の通りです。

順方向電流ゲインを定めるパラメータ ⇒IS,BF,NF,ISE,IKF,NE

逆方向電流ゲインを定めるパラメータ ⇒BR,NR,ISC,IKF,NC

順方向及び逆方向領域の出力コンダクタンスを定めるパラメータ ⇒VAF,VAR

抵抗(RB,RC,RE)、但し、RBは大電流依存性を持つ事が可能であります。

ベース電荷蓄積の影響はキャリアのベース領域走行時間(TF,TR)と接合容量(CJ,VJ,MJ)による非線型空乏層容量で定義されています。

また、トランジスタのデバイスモデリングはデバイスモデリングの基礎でもあります。デバイスモデリング教材(BJT編):[21,000円]を提供しています(Fig.3)。是非、ご活用下さい。詳細は、http://beetech.web.infoseek.co.jp/products/material/material\_05.htmlをご参照下さい。デバイスモデリング教材は、現在、9種類のラインナップでご提供しています。

Fig.3 デバイスモデリング教材(BJT編)

### デバイスモデル

## [CCFL]

Cold Cathode Fluorescent Lamp

CCFLは、冷陰極管 (Cold Cathode Fluorescent Lamp)です。バックライトの需要で急激に伸びてきたデバイスです。ビー・テクノロジーにおいては、ドライバICとCCFLセットでのモデル提供及びドライブ回路+CCFLセットでのシミュレーションとしてご提供しています。前者の場合、多くの時間をCCFLドライバICのモデリングに費やします。ICのモデリングの特徴は、ブロック図から1つ1つ等価回路図を作成し、電気的特性を評価していきます。

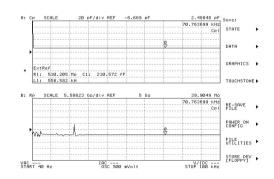

CCFL自体のモデリングは、CCFL自体のインピーダンス特性(インピーダンス|Z| vs. 周波数)のデータをベースに等価回路を作っていきます。Fig.4はインピーダンス特性図です。Cp及びRpを測定しています。測定機器は、Agilent 4294Aです。そして、Fig.5の右側の等価回路図の最適な定数を決定しながら、シミュレーションを行い、評価検証をしていき、モデルの精度を向上させていきます。

Fig.4 CCFLのインピーダンス特性図

CCFLについて理解する場合、NECライティングのサイトがわかり易く解説しています。URLは、http://www.nelt.co.jp/products/ccfl/about.htmlです。CCFLは、バックライトに使用され、皆様の身近な電気製品(ノートPC、ディスプレイ)に格納されています。

Fig.5 CCFLのアプリケーション回路図

## 回路解析 シミュレーション

## [PFC回路方式]

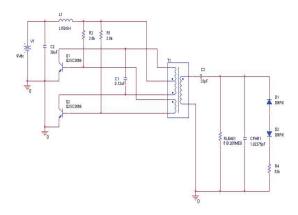

PFCとは、Power Factor Correctionの略で「力率改善回路」のことを言います。PFC回路につきましては、各種技術参考書にてご理解下さい。全体回路図は複雑ですが、今回はキー・デバイス、2個に絞ります。U1のSiCSBD、Q2のSiBJTです。Q2のトランジスタは、順方向及び逆方向特性に再現性を持たせたGummel-Poonモデル(vol.007である本号のデバイスモデルでご紹介しています)です。今回のシミュレーションを行うPFC回路の回路図は、Fig.6の通りです。採用したモデルは下記の通りです。

U1,SiC SBD, CSD10060A (CREE社) Q2, Si BJT,2SC6113 (三洋半導体)

CREE社はシリコンカーバイドのデバイスで知られる半導体メーカーです。現在の組み合わせは、SiC SBD+Si BJTですが、パワー・エレクトロニクスにおいては、SiC SBD+SiC BJTに移行していく流れだと推測出来ます。PFC回路方式にて、シミュレーションを行う顧客の殆どは、過渡解析における損失計算が殆どです。今回のシミュレーション条件は下記の通りです。

Vce=200V IB1=0.64A, IB2=-1.28A Duty Cycleは1%以下です。

Fig.6 PFC回路図(PSpice Capture)

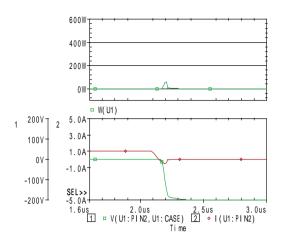

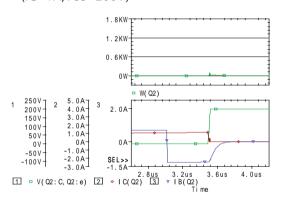

Fig.7 SiC SBD Trrシミュレーション (IF=1A,VR=200V)

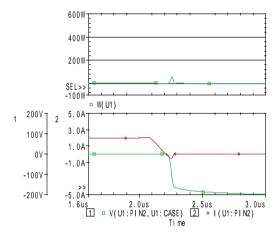

Fig.8 SiC SBD Trrシミュレーション(IF=2A.VR=200V)

Fig.7及びFig.8にSiC SBDの逆回復特性のシミュレーションです。3条件のシミュレーションを行いました。1ケースの条件(IF=4A,VR=200V)は、紙面の関係上省略しています。シミュレーションにより、損失ピークを求めました。

### CSD10060A(SiC SBD)

IF=1A,VR=200V-->P\_loss(peak)=58.416W IF=2A,VR=200V-->P\_loss(peak)=58.063W IF=4A,VR=200V-->P\_loss(peak)=43.426W 次にトランジスタ側をシミュレーションで検証していきます。トランジスタの場合、Turn-On側とTurn-Off側でのシミュレーションが必要になります。

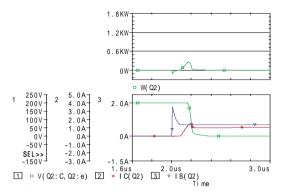

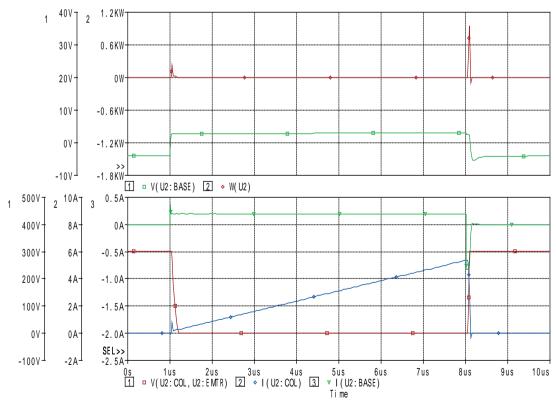

Fig.9 2SC6113 Turn-Onシミュレーション(IC=1A,Vce=200V)

Fig.10 2SC6113 Turn-Offシミュレーション (IC=1A,Vce=200V)

Fig.9に Turn-Onシミュレーション、Fig.10に Turn-Offシミュレーションを掲載しました。条 件を変更し、6ケースについてシミュレーション しました。

[Turn-on] (1)IC=1A,Vce=200V P\_loss(peak)=250.179W Tr=40.774ns Ton=217.383ns

このデバイスは優れている事が解りました。

[Turn-on] (2)IC=2A,Vce=200V P\_loss(peak)=440.036W Tr=50.593ns Ton=285.883ns

(3)IC=4A,Vce=200V P\_loss(peak)=0.831kW Tr=55.120ns Ton=415.411ns

[Turn-off] (1)IC=1A,Vce=200V P\_loss(peak)=72.232W Tf=21.097ns Toff=504.105ns

(2)IC=1A,Vce=200V P\_loss(peak)=231.317W Tf=71.943ns Toff=447.950ns (3)IC=4A,Vce=200V P\_loss(peak)=620.886W Tf=79.832ns Toff=259.577ns

です。これらは、常温のシミュレーション結果です。このデータをリファレンス値とし、それぞれに高温のモデル(TC=150°Cモデル等)を使用すれば、高温時の損失計算は算出出来ます。シミュレーションの場合、過渡解析を行い、損失の計算は非常に簡単に出来ます。これらの手法で、損失を減らす(エコ設計)ような回路設計をSPICEシミュレーションで行う事で理論的で裏付けのあるデザインが出来ます。

Fig.11に他のPFC回路方式のシミュレーションのケースを掲載します。青色ラインが、BJTのIC波形ですが、シミュレーションにより、SiC SBDのtrrを改善する事で、同時にIC波形も改善し、損失も減らせる事が解りました。1つのテンプレートを作成すれば色々な分析をする事が出来ます。

Fig.11 PFCシミュレーション結果(他の例)

デバイスの場合、温度環境と言えば3種類ある。TC->ケース温度、Ta->周囲温度、Tj->ジャンクション温度(接合温度)である。接合温度の測定は、 物理的に困難であるため、シミュレーションの世界では、TCモデルかTaモデルが一般的である。

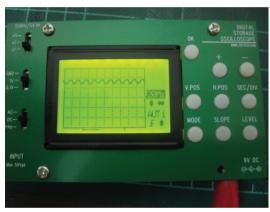

### 道具箱 オシロスコープ・キット

オシロスコープの動作原理を学ぶ。

最近、秋月電子にて、オシロスコープのキット([K-03144]SMD実装済:5,700円)が販売されました。500Hz/5V ppですので、業務には使用出来ませんが、動作周波数が低いアナログシンセの世界では何とか使用出来ると思います。ICにてブラックボックス化されていますが、実際に組み立てて、動作を学習するのには良いかも知れません。SMD実装済のキットなので、1時間程度で組み立て可能です。また、自分で工夫して、使いやすいプローブを製作するのも面白いです。

### 外部セミナー情報

- (1) Japan ANSYS Conference 2009

- (2) PSpiceアプリケーションセミナー

- (1) Japan ANSYS Conference 2009

2009年11月20日(金) に ザ・プリンスパーク タワー東京にて、Japan ANSYS Conferenceが 開催されます。16:05-16:35のG-6にて、「Simplorerモデルのデバイスモデリング」を 発表致します。詳細は、http://www.event-info.com/2009jac/program.phpをご参照下さい。

(2)PSpiceアプリケーションセミナー

2009年12月3日(木曜日)13:30-17:00にサイバネットシステム株式会社にて、セミナーを開催します。3部構成で、ビー・テクノロジーは1,2部にて講演致します。

#### 【1部】

1.デザインキットの活用方法1.1デザインキットのコンセプト1.2デザインキットのロードマップ1.3電源回路方式の紹介1.4最新デザインキットの紹介 D級アンプ回路 擬似共振回路

### 【2部】

2.最新のシミュレーション事例2.1 太陽電池シミュレーション2.2 リチウムイオン電池のシミュレーション2.3 事例: 太陽電池+リチウムイオン電池シミュレーション

3部は、サイバネットシステムが講演します。

皆様のご参加、お待ちしております。

Bee Style: Volume 007 2009年11月1日 発行

編 者:株式会社ビー・テクノロジー

発行人:堀米 毅

郵便番号105-0012 東京都港区芝大門二丁目2番7号 7セントラルビル4階

Tel (03)5401-3851 (代表)

Fax (03)5401-3852

電子メール info@bee-tech.com

All Rights Reserved copyright (C) Bee Technologies Inc.